Please select your location and preferred language where available.

創新技術,為更高容量鋪路

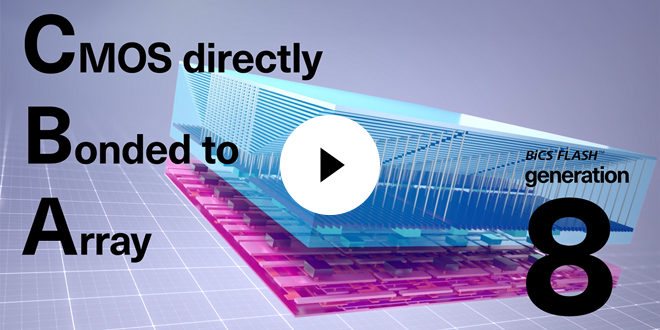

支援當代 BiCS FLASH™ 產品重大躍進的是多項突破性技術創新。透過快閃記憶體工程設計和組裝流程的持續精進,實現了密度、效能和電源效率的全面提升。深入了解 CMOS 直接鍵合陣列(CBA)、On Pitch Select Gate (OPS)、OPS 和 32 晶粒記憶體組裝如何共創 3D 快閃記憶體的未來。

前端製程技術

專訪

利用高精度晶圓鍵合技術的高密度 3D 快閃記憶體,為儲存帶來全新價值

近年來,快閃記憶體製造商主要聚焦於開發增加記憶體單元層數以及提升儲存密度的技術。每當新一代快閃記憶體問世,層數便隨之增加,部分產品甚至已突破 200 層。

然而,正如鎧俠記憶體事業部副總裁 井上敦史(Atsushi Inoue)所言:「增加記憶體單元層數只是提升容量與儲存密度的方式之一,而我們並非只專注於層數的多寡。」

OPS 技術

傳統意義上,記憶體單元(Memory Cells)之間存在著不具功能的「虛設(Dummy)」區域,導致儲存密度降低。透過 OPS 技術消除了這些不必要的虛設區域,使相同空間內得以配置更多實際的記憶體單元,從而大幅提升儲存密度。

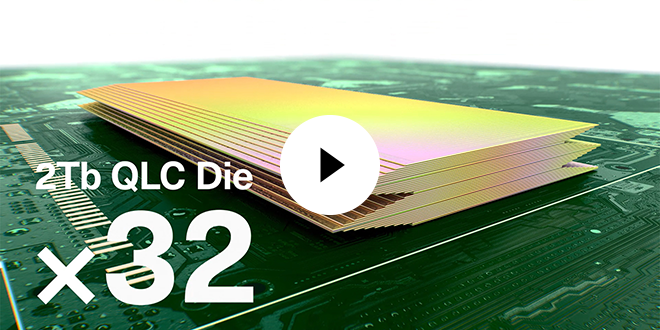

後端製程組裝技術

專訪

以創新 2mm 快閃記憶體組裝技術引領 AI 進化

32 顆記憶體晶粒組裝於單一封裝內

AI 快速成長加速了對快閃記憶體容量的需求。鎧俠成功將 32 顆 2TB (兆位元) 記憶體晶粒組裝於高度小於 2mm 的單一封裝內,開發出大容量 8TB(兆位元組)快閃記憶體。這項成就得益於先進的組裝製程技術,包括將晶圓研磨至極薄程度的技術。

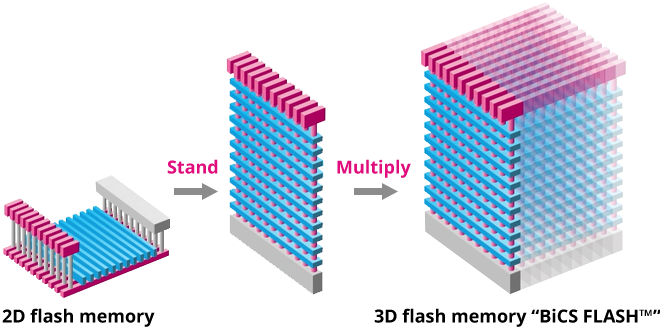

各世代共通的 BiCS FLASH™ 基礎技術

BiCS FLASH™ 3D 快閃記憶體透過垂直堆疊記憶體單元,大幅提升了儲存密度。這種摩天大樓式的架構克服了 2D(平面)快閃記憶體僅能以並排方式排列單元的限制。透過增加單元間距,不但可降低單元間的干擾,相較於 2D 快閃記憶體,進而實現更優異的密度、效能和電源效率表現。

TLC (三層單元)和 QLC(四層單元)技術

BiCS FLASH™ 3D 快閃記憶體產品線同時包含每單元 3 位元(TLC)與每單元 4 位元(QLC)技術。QLC 技術將每個記憶體單元的資料位元數從 3 位元提升至 4 位元,大幅提升了儲存容量。

利用 BiCS FLASH™ QLC 技術,在 16 層晶片堆疊架構下,單一封裝內即可實現高達 4TB 的容量。

鎧俠是業界首批預見並為儲存技術成功轉型做足準備的廠商之一,推動 SLC 到 MLC、從 MLC 到 TLC,以及從 TLC 到 QLC 的演進歷程。

鎧俠 QLC 技術是需要高密度、低成本儲存解決方案應用的理想選擇。現今的 QLC 技術,憑藉單一封裝所能實現的最高可用密度,有效縮減了空間占用,使儲存解決方案得以大規模擴展。

產品應用

無論是車用,輕巧高效能的個人電腦或是雲端伺服器以及超大規模資料中心部署,鎧俠記憶體和儲存解決方案透過提供先進的高效能、高密度、低功耗、低延遲、可靠性等功能,實現新興應用的成功,並讓現有技術發揮其可預期的潛力。

支援

如果您有任何技術疑問、想了解更多訊息、對樣品或採購商用產品(記憶體晶片、SSD)有興趣,請與我們聯繫。