Please select your location and preferred language where available.

鎧俠研發核心技術,協助實現高密度、低功耗 3D DRAM 的實作

展示高度可堆疊的氧化物半導體通道電晶體技術

- 2025 年 12 月 12 日

- 鎧俠株式會社

全球記憶體解決方案領導廠商鎧俠株式會社,今日宣布開發高度可堆疊的氧化物半導體通道電晶體,這將有助於高密度、低功耗 3D DRAM 的實作。這項技術於 12 月 10 日在美國舊金山舉行的 IEEE 國際電子元件會議 (IEDM) 上發表,具有降低各種應用所需功耗之潛力,包括 AI 伺服器和 IoT 元件。

在 AI 時代,對容量更大、功耗更低且可以處理大量資料的 DRAM 需求不斷成長。傳統 DRAM 技術已逼近記憶體單元大小擴充的實體限制,促進對記憶體單元 3D 堆疊之相關研究,以期能夠獲得額外容量。若依照傳統 DRAM 情況,使用單晶矽作為堆疊記憶體單元中的電晶體通道材料,將會提高製造成本,更新記憶體單元所需的功率也會隨著記憶體容量成比例增加。

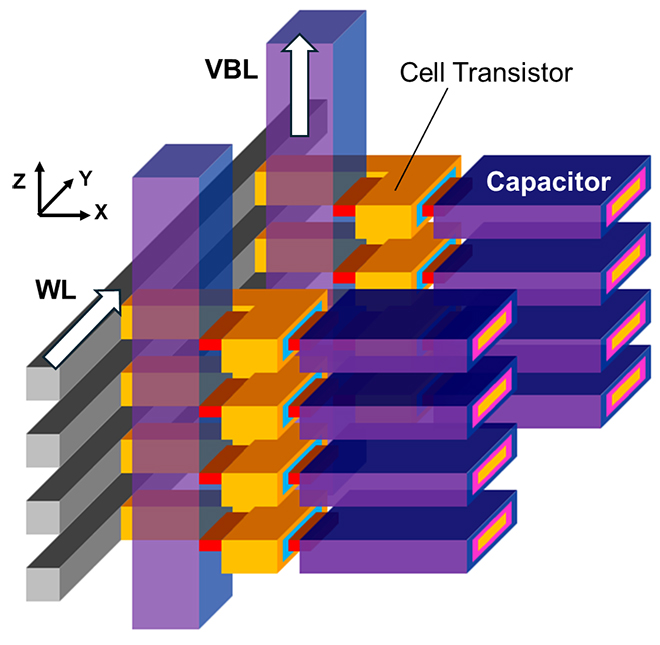

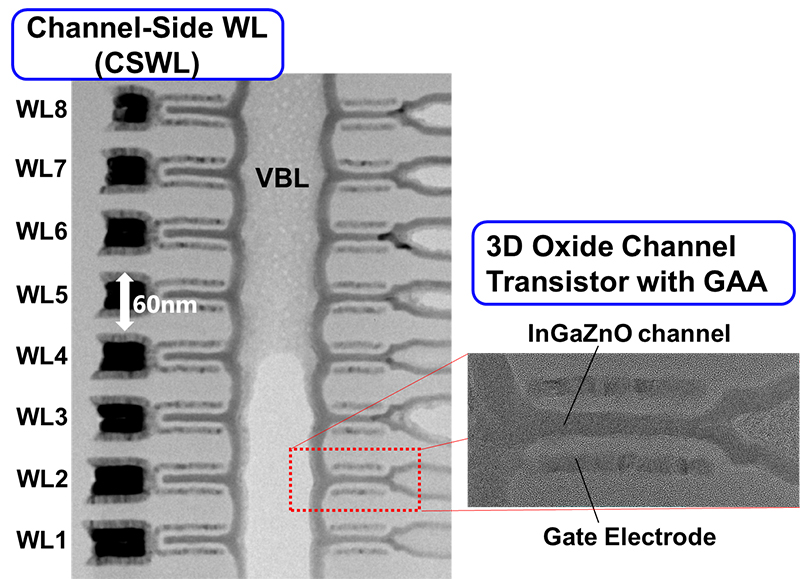

在去年的 IEDM 上,我們宣布開發了氧化物半導體通道電晶體 DRAM (OCTRAM),此技術使用由氧化物半導體製成的垂直電晶體。在今年的簡報中,我們展示了高度可堆疊氧化物半導體通道電晶體,此技術實現了 OCTRAM 的 3D 堆疊,驗證八層堆疊的電晶體操作。

此新技術堆疊成熟的氧化矽及氮化矽膜,並以氧化物半導體 (InGaZnO) 取代氮化矽區,以同時形成水平堆疊電晶體的垂直層。我們還推出了一種新型 3D 記憶體單元結構,能夠擴展垂直間距。這些製程和結構預期將能克服實現記憶體單元 3D 堆疊的成本挑戰。

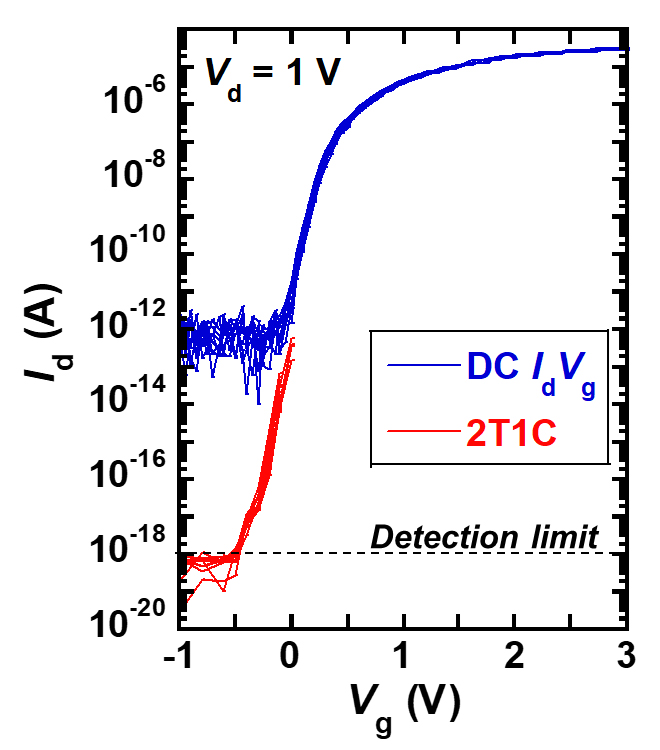

此外,由於氧化物半導體的低關電流特性,預期可降低更新功率。我們已經證明,對於取代過程所形成的水平電晶體,具有高開電流 (>30μA) 和超低關電流 (<1aA,10^-18A) 的能力。此外,我們已成功製造出水平電晶體的 8 層堆疊,並確認該結構內電晶體的成功操作。

在鎧俠株式會社,我們將持續研發此技術,以在實際應用中實現 3D DRAM 部署。

- This announcement has been prepared to provide information on our business and does not constitute or form part of an offer or invitation to sell or a solicitation of an offer to buy or subscribe for or otherwise acquire any securities in any jurisdiction or an inducement to engage in investment activity nor shall it form the basis of or be relied on in connection with any contract thereof.

- Information in this document, including product prices and specifications, content of services and contact information, is correct on the date of the announcement but is subject to change without prior notice.