Please select your location and preferred language where available.

鎧俠開發全新 3D 半圓形快閃記憶體單元結構 「Twin BiCS FLASH」

- 利用創新分離閘極技術提高位元密度 -

- 2019 年 12 月 12 日

- 鎧俠株式會社

【東京訊】鎧俠株式會社今日宣布開發全球首款[1] 3D 半圓形分離閘極快閃記憶體單元結構「Twin BiCS FLASH」,採用特別設計的半圓形浮動閘極 (FG) 單元。Twin BiCS FLASH 可實現卓越的寫入斜率和更寬的寫入/抹除窗口,且比起傳統的圓形電荷捕捉 (CT) 單元占用更小的單元尺寸。這些特質讓這種新的單元設計,有望超越每單元四位元 (QLC) 成為有力候選方案,大幅提高記憶體密度並減少堆疊層。這項技術於 12 月 11 日在加州舊金山舉辦的 IEEE 國際電子元件會議 (IEDM) 上發表。

3D 快閃記憶體技術已能透過減少單元堆疊層數量,以及應用多層堆疊沉積和高長寬比蝕刻,以更低的每位元成本實現更高的位元密度。近年來,隨著單元層的數量超過 100,衡量蝕刻剖面控制、尺寸一致性和生產率之間的取捨變得格外具有挑戰性。為了克服這道難題,鎧俠設計出一種新的半圓形單元,將傳統圓形單元的閘極電極分裂以減少單元尺寸,進而利用更少的單元層實現更高的記憶體密度。

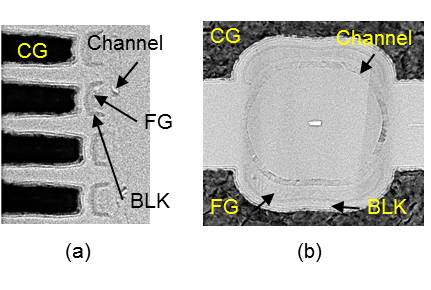

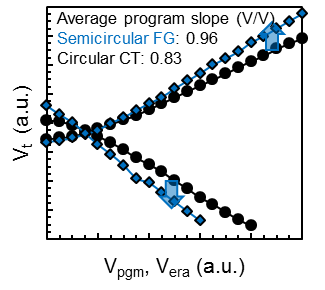

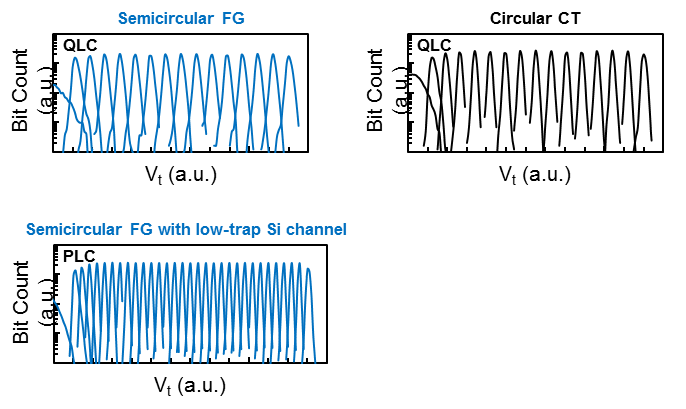

受到曲率效應影響,可以增強透過穿隧介電層的載子注入,同時減少區塊 (BLK) 介電層的電子洩漏,因此相較於平面閘極,圓形控制閘極能提供更寬的寫入窗口,並減緩飽和問題。在這種分離閘極的單元設計中,圓形控制閘極分成對稱的兩個半圓形閘極,可充分利用大幅改善的寫入/抹除動態平衡。如圖 1 所示,導電儲存層與高 k BLK 介電層結合,藉此提升電荷捕捉效率,達到高耦合比,以增加寫入窗口並減少 FG 的電子洩漏,從而減緩飽和問題。圖 2 中的實驗寫入/抹除特性指出,相較於大尺寸的圓形 CT 單元,具備高 k BLK 的半圓形 FG 單元可顯著增強寫入斜率和寫入/抹除窗口。半圓形 FG 單元擁有卓越的寫入/抹除特性,可望以較小的單元尺寸獲得相對緊密的 QLC Vt 分布。此外,低捕捉 Si 通道的整合可實現每單元超過四位元,如圖 3 所示的五層單元 (PLC)。由上述結果證實,半圓形 FG 單元是追求更高位元密度的可行選項。

展望未來,鎧俠將在快閃記憶體的創新研發上繼續開發 Twin BiCS FLASH,並找出如何實際應用。在 2019 年 IEDM 上,鎧俠也發表了其他六篇論文,介紹該公司在快閃記憶體領域的密集研發活動。

[1] 資料來源:鎧俠株式會社,以 2019 年 12 月 12 日資料為準。