Please select your location and preferred language where available.

東芝記憶體株式會社開發出全新橋接晶片,利用 PAM 4 提升固態硬碟速度和容量

- 2019 年 2 月 21 日

- 東芝記憶體株式會社

【東京訊】全球記憶體解決方案領導廠商東芝記憶體株式會社,今日宣布成功開發可實現高速、大容量固態硬碟的橋接晶片。該公司利用所開發的小型、低耗電量橋接晶片,比傳統無橋接晶片使用更少的高速訊號線,成功連接更多快閃記憶體晶片。這項成果已發佈於 2 月 20 日在舊金山舉行的 2019 年國際固態電路研討會 (ISSCC 2019)。

在固態硬碟中,多個快閃記憶體晶片需連接至管理運行的控制器。隨著越多快閃記憶體晶片連接至控制器介面,運行速度會下降,因此能夠連接的晶片數量有限。若要提升容量,就必須增加介面的數量,但這會導致連接至控制器的高速訊號線數量過多,使得固態硬碟電路板的配線變得更加困難。

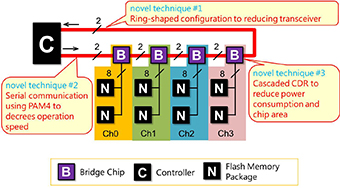

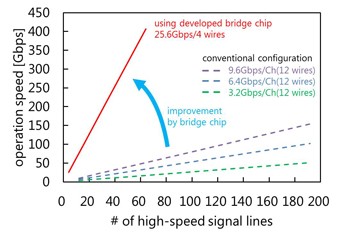

該公司利用可連接控制器和快閃記憶體晶片的橋接晶片 (圖 1) 克服了這個問題,其中包含三種新技術:菊鏈*1 連接,以環狀方式連接控制器和橋接晶片;採用 PAM 4*2 的序列通訊;以及抖動 (jitter)*3 改善技術,不再需要在橋接晶片使用 PLL 電路*4。憑藉以上技術,能夠減少橋接晶片的開銷,而且僅需透過幾條高速訊號線,就能高速運行大量的快閃記憶體晶片 (圖 2)。

橋接晶片和控制器的環狀結構,可將橋接晶片需要的收發器數量從兩對減少至一對,縮小橋接晶片的面積。此外,在控制器和菊鏈式橋接晶片之間採用 PAM 4 序列通訊,可降低橋接晶片電路的運行速度和所需效能。全新 CDR*5 可利用 PAM 4 的特性來改善抖動特性,讓橋接晶片中不再需要安裝 PLL 電路,進而達到減少晶片面積和耗電量的效果。

原型橋接晶片採用 28nm CMOS 製程,並以環狀菊鏈方式連接四個橋接晶片與一個控制器,藉此評估成果。經過證實,在 25.6 Gbps 速度下,所有橋接晶片和控制器都擁有良好的 PAM 4 效能,且可達到低於 10-12 的 BER*6。

展望未來,東芝記憶體將進一步加強橋接晶片效能,並減少晶片面積與耗電量,以持續開發前所未見的高速、大容量儲存技術。

備註

*1菊鏈:將多個晶片按順序連接的方式

*2PAM 4:4 級脈幅調變 (包含 4 數值資料)

*3抖動 (jitter):時脈或訊號波形時域的波動

*4PLL:鎖相迴路 (產生準確參考訊號的電路)

*5CDR:時脈資料回復 (從接收訊號還原資料與時脈的電路)

*6BER:位元錯誤率 (數值越低,效能越佳)